计算机组成原理

计算类

浮点数加减

变形补码

- 两个数字相异为溢出

IEEE754 标准

- 符号位 S(1 位):0 为正,1 为负

- 阶码 E(8 位/11 位): 是一种移码 ,就是把最小的负数变成 0,这样就可以表示负数但不使用符号位。真值+ 是这一部分的二进制代码

- 尾数 M:它的二进制值为

特殊情况:

- E=255,M=0,结果为无穷大

- E=255,M!=0,结果为 NaN

- E=0,M=0,结果为 0,分正负

- E=0,M!=0,结果用 表示

速记:阶码为 0,,否则

科学计数法表示 用

浮点数加减法

判断是否为 0

对阶,小阶看大阶

尾数加减

结果规格化

存储器性能指标

带宽:一定时间传输的数据量

顺序存储器:设模块数为,模块读取一个字周期为,则总时间:

交叉存储器:设模块数为,总线传送周期为,模块读取一个字周期为,则总时间:

读取数据总量:

Cache 性能指标

为 cache 完成的总次数, 为主存完成的总次数; 为命中访问时间, 为未命中访问时间

命中率:

平均访问时间:

访问效率(命中时间/平均时间):

流水线性能指标

- 时空图

- 实际吞吐率:指令数/总时间

- 加速比:非流水线用时/流水线用时

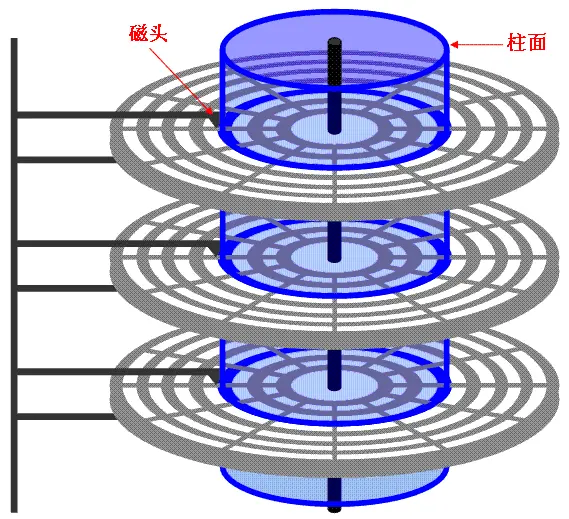

硬磁盘性能指标

记录面:磁盘表面,双向

柱面:磁道的数目

存储密度:

- 道密度:沿着半径,单位长度磁道数,道/英寸

- 位密度:单位磁道长度记录的二进制代码,位/英寸

- 面密度:位密度 * 道密度

单磁道容量,D 为位密度

存储容量计算:

平均寻址时间:找道时间、寻区时间

平均存取时间:平均找道时间 +平均寻区时间 +数据传输时间

- r: 磁盘旋转速率

- N: 每磁道字节数

- b: 传送的字节数

数据传输率:,其中 D 为位密度,v 为线速度,n 为转速,N 为每磁道容量

分析类

存储器拓展

- 选模块:高位地址

- 算芯片个数:存储量换算到位,再相除

- 画图:地址总线、数据总线、译码器

分析指令格式

看字长:单字长、双子长

几地址:看地址个数

类型:RR(仅访问寄存器)、RS(访问寄存器、存储器)、SS(仅访问存储器)

操作个数:

寻址方式:

| 寻址方式 | 说明 |

|---|---|

| 立即寻址 | 操作数直接在指令中 |

| 寄存器寻址 | 操作数在寄存器 |

| 直接寻址 | 操作数的地址在指令中 |

| 寄存器间接寻址 | 操作数的地址在寄存器中 |

| 间接寻址 | 操作数的地址在存储器中 |

| 相对寻址 | 操作数的地址为 PC+偏移量 |

| 基址寻址 | 操作数的地址在基址寄存器 |

| 基址变址寻址 | 操作数的地址=变址寄存器+偏移量 |

处理器

指令流水线

- 时空图

- 实际吞吐率:指令数/总时间

- 加速比:非流水线用时/流水线用时

设计类

存储器组成

同分析:存储器拓展

数据通路

- 数据总线

- 暂存器->ALU

- DR 和主存双向

- AR 和主存单向

- ALU->PC 加一

指令格式设计

- 操作码个数:决定 OP 长度

- 寻址方式:决定长度

- 操作数个数:单地址、双地址

- 指令长度:单字、双字,决定指令长度

微指令、微程序控制器设计

微程序控制器组成:

- 控制存储器:存放微程序、只读

- 地址转移逻辑:存放下一条指令的地址

- 微指令寄存器:存放控制存储器读出的一条指令

设计微指令:

- 水平型:控制字段、判别测试字段(一个转移条件 1 位)、下地址字段(同控存容量)

- 垂直型:微操作码、原寄存器、目标寄存器、其他

微地址形成方法:

- 计数器方式:后继微地址采用现行微地址加上增量

- 多路转移方式:按判别测试和状态条件选择后续的微地址

指令执行流程

- 标题: 计算机组成原理

- 作者: ObjectKaz

- 创建于: 2021-06-21 12:37:08

- 更新于: 2023-05-25 17:17:00

- 链接: https://www.objectkaz.cn/053461bec650.html

- 版权声明: 本文章采用 CC BY-NC-SA 4.0 进行许可。